**ÉCOLE DOCTORALE MATHÉMATIQUES, INFORMATIQUE,

PHYSIQUE THÉORIQUE ET INGÉNIERIE DES SYSTÈMES**

LABORATOIRE D'INFORMATIQUE FONDAMENTALE D'ORLÉANS

LABORATOIRE DE SÛRETÉ ET SÉCURITÉ DES LOGICIELS, CEA LIST

**THÈSE** présentée par :

**Allan BLANCHARD**

soutenue le : 6 Décembre 2016

pour obtenir le grade de : **Docteur de l'université d'Orléans**

Discipline : **Informatique**

**Aide à la vérification de programmes concurrents par

transformation de code et de spécifications**

**THÈSE DIRIGÉE PAR :**

**Frédéric LOULERGUE** Professeur, Université d'Orléans

**RAPPORTEURS :**

**Catherine DUBOIS** Professeur, ENSIIE

**Sylvain CONCHON** Professeur, Université Paris-Sud XI

**JURY :**

**Sébastien LIMET** Professeur, Université d'Orléans, Président

**Nikolai KOSMATOV** Ingénieur-Chercheur, CEA List, Encadrant

**Stephan MERZ** Directeur de Recherche, INRIA, Examinateur

**Jan-Georg SMAUS** Professeur, Université de Toulouse, Examinateur

**Louis RILLING** Ingénieur, DGA, Examinateur

**ÉCOLE DOCTORALE MATHÉMATIQUES, INFORMATIQUE,

PHYSIQUE THÉORIQUE ET INGÉNIERIE DES SYSTÈMES**

LABORATOIRE D'INFORMATIQUE FONDAMENTALE D'ORLÉANS

LABORATOIRE DE SÛRETÉ ET SÉCURITÉ DES LOGICIELS, CEA LIST

**THÈSE** présentée par :

**Allan BLANCHARD**

soutenue le : 6 Décembre 2016

pour obtenir le grade de : **Docteur de l'université d'Orléans**

Discipline : **Informatique**

**Aide à la vérification de programmes concurrents par

transformation de code et de spécifications**

# REMERCIEMENTS

O

Je remercie tout d'abord Catherine Dubois et Sylvain Conchon pour avoir accepté de rapporter ma thèse, ainsi que Stephan Merz, Jan-Georg Smaus et Louis Rilling pour avoir accepté d'examiner mes travaux. Merci également à Sébastien Limet pour avoir présidé mon jury de thèse. Un grand merci à Nikolai Kosmatov et Frédéric Loulergue pour leur disponibilité et leurs conseils, ainsi que pour avoir témoigné autant d'intérêt pour mes travaux tout au long de ces 3 années. Je remercie tous les membres du jury pour leurs commentaires et questions qui m'ont permis d'améliorer le présent manuscrit et de préparer le futur de ces travaux.

Avant d'entamer une thèse, il y a les études et on y fait des rencontres. On rencontre notamment des enseignants qui donnent envie d'aller plus loin, d'en apprendre plus. Un grand merci donc aux enseignants que j'ai pu avoir pendant mes cinq années d'étude à l'IUT puis à la Faculté et qui ont su transmettre cette envie. Merci notamment à Sylvain Jubertie, sans qui je ne me serai probablement pas engagé sur ce chemin.

Un grand merci à tous les membres du LSL, pour leur accueil, leur envie de partager (et confronter !) les connaissances. Merci à David Bühler, avec qui nous avons partagé un bureau pendant ces trois années de thèse, dont quelques mois de course à la rédaction, le soutien mutuel c'est une bonne aide pour avancer. Merci aux membres de l'équipes FRAMA-C pour la précieuse aide qu'ils m'ont fournie dans l'utilisation, parfois complexe admettons-le, de leur outil. N'en déplaise à certaines mauvaises langues : « *ça marche, et ça continuera de marcher* ».

Merci à ma famille pour m'avoir toujours soutenu et encouragé dans mes choix et pour leur précieuse présence pendant ces trois années. Merci également à tous mes amis avec qui il est toujours bon, le temps d'un week-end, de se détendre ensemble et d'oublier tout le reste.

Comment terminer, finalement, sans remercier Mélina, qui partage ma vie depuis plus de 10 ans maintenant et qui a su continuer à me supporter pendant ces trois années, *y compris* pendant les dernières semaines de rédaction. Je pense que je n'aurai jamais ni le temps ni les mots pour lui dire assez merci.

# TABLE DES MATIÈRES

|                                                                        |      |

|------------------------------------------------------------------------|------|

| REMERCIEMENTS                                                          | iii  |

| TABLE DES MATIÈRES                                                     | v    |

| LISTE DES FIGURES                                                      | viii |

| 1 INTRODUCTION                                                         | 1    |

| 1.1 CORRECTION DES PROGRAMMES . . . . .                                | 3    |

| 1.2 PREUVE DE PROGRAMMES . . . . .                                     | 5    |

| 1.3 CONCURRENCE . . . . .                                              | 7    |

| 1.4 PROPOSITION . . . . .                                              | 10   |

| 2 ÉTAT DE L'ART                                                        | 13   |

| 2.1 MÉTHODES DE VÉRIFICATION . . . . .                                 | 14   |

| 2.1.1 Test . . . . .                                                   | 14   |

| 2.1.2 Interprétation abstraite . . . . .                               | 15   |

| 2.1.3 Model-Checking . . . . .                                         | 15   |

| 2.1.4 Logiques de Hoare . . . . .                                      | 16   |

| 2.1.5 Logique de séparation . . . . .                                  | 17   |

| 2.2 PROGRAMMES CONCURRENTS . . . . .                                   | 18   |

| 2.2.1 Méthode de Hoare . . . . .                                       | 19   |

| 2.2.2 Méthode d'Owicki-Gries . . . . .                                 | 20   |

| 2.2.3 Rely-Guarantee . . . . .                                         | 21   |

| 2.2.4 Logique de séparation concurrente . . . . .                      | 22   |

| 2.2.5 Combinaison de Rely-Guarantee et logique de séparation . . . . . | 22   |

| 2.3 OUTILS D'ANALYSE DE CODE C . . . . .                               | 23   |

| 2.3.1 FRAMA-C . . . . .                                                | 23   |

| 2.3.2 VCC . . . . .                                                    | 25   |

| 2.3.3 VERIFAST . . . . .                                               | 26   |

| 2.4 MODÈLES MÉMOIRE FAIBLES . . . . .                                  | 27   |

| 2.4.1 Formalisations . . . . .                                         | 27   |

|          |                                                                  |           |

|----------|------------------------------------------------------------------|-----------|

| 2.4.2    | Identification d'exécutions . . . . .                            | 28        |

| 2.4.3    | Logiques . . . . .                                               | 29        |

| 2.4.4    | Retrouver le modèle séquentiellement consistant . . . . .        | 29        |

| <b>3</b> | <b>ÉTUDE DE CAS : MODULE D'ADRESSAGE</b>                         | <b>31</b> |

| 3.1      | INTRODUCTION . . . . .                                           | 31        |

| 3.2      | MODULE D'ADRESSAGE VIRTUEL D'ANAXAGOROS . . . . .                | 33        |

| 3.3      | VÉRIFICATION FORMELLE . . . . .                                  | 35        |

| 3.3.1    | Simulation des exécutions parallèles . . . . .                   | 36        |

| 3.3.2    | Compteurs de références et invariants globaux . . . . .          | 38        |

| 3.3.3    | Preuve avec le greffon Wp de Frama-C . . . . .                   | 42        |

| 3.3.4    | Preuve de lemmes avec Coq . . . . .                              | 44        |

| 3.4      | DISCUSSION . . . . .                                             | 46        |

| 3.4.1    | Correction des hypothèses . . . . .                              | 46        |

| 3.4.2    | Bénéfices et limitations constatés . . . . .                     | 47        |

| 3.5      | À PROPOS DE LA PREUVE D'OS . . . . .                             | 49        |

| 3.5.1    | Preuve interactive . . . . .                                     | 49        |

| 3.5.2    | Preuve automatique . . . . .                                     | 50        |

| 3.5.3    | Anaxagoros . . . . .                                             | 51        |

| 3.6      | CONCLUSION . . . . .                                             | 52        |

| <b>4</b> | <b>TRANSFORMATION AUTOMATIQUE DE CODE</b>                        | <b>55</b> |

| 4.1      | INTRODUCTION . . . . .                                           | 55        |

| 4.2      | FONCTIONNALITÉS DU GREFFON CONC2SEQ . . . . .                    | 56        |

| 4.2.1    | Exemple : simple écrivain, multiples lecteurs . . . . .          | 57        |

| 4.2.2    | Variables globales locales au fil d'exécution . . . . .          | 59        |

| 4.2.3    | Primitives atomiques . . . . .                                   | 59        |

| 4.2.4    | Fonctions et blocs atomiques . . . . .                           | 62        |

| 4.2.5    | Réduction sur les fils d'exécution . . . . .                     | 64        |

| 4.2.6    | Invariant global . . . . .                                       | 65        |

| 4.3      | PRODUCTION DU CODE SIMULANT SPÉCIFIÉ . . . . .                   | 65        |

| 4.3.1    | Contexte d'exécution . . . . .                                   | 66        |

| 4.3.2    | Actions atomiques, entrée de fonctions, entrelacements . . . . . | 68        |

| 4.3.3    | Spécifications . . . . .                                         | 74        |

| 4.4      | TRADUCTION DU <i>built-in thread_reduction</i> . . . . .         | 75        |

| 4.4.1    | Passage au premier ordre . . . . .                               | 75        |

| 4.4.2    | Génération des prédictats et lemmes . . . . .                    | 77        |

| 4.5      | DISCUSSION . . . . .                                             | 79        |

|                                                           |            |

|-----------------------------------------------------------|------------|

| 4.6 CONCLUSION . . . . .                                  | 82         |

| <b>5 PREUVE DE LA MÉTHODE DE TRANSFORMATION</b>           | <b>83</b>  |

| 5.1 INTRODUCTION . . . . .                                | 83         |

| 5.2 LANGAGE SIMPLIFIÉ . . . . .                           | 85         |

| 5.2.1 États de l'exécution et actions . . . . .           | 87         |

| 5.2.2 Sémantiques de programmes . . . . .                 | 89         |

| 5.3 TRANSFORMATION . . . . .                              | 92         |

| 5.3.1 Affectation locale et partagée . . . . .            | 94         |

| 5.3.2 Sauts conditionnels . . . . .                       | 96         |

| 5.3.3 Appel de méthode et retour . . . . .                | 97         |

| 5.3.4 Section atomique . . . . .                          | 99         |

| 5.3.5 Transformation d'une instruction . . . . .          | 99         |

| 5.3.6 Entrelacements . . . . .                            | 101        |

| 5.3.7 Définition du programme simulant . . . . .          | 103        |

| 5.4 ÉQUIVALENCE DES EXÉCUTIONS . . . . .                  | 103        |

| 5.4.1 Équivalence d'états et de traces . . . . .          | 103        |

| 5.4.2 Correction de la simulation . . . . .               | 106        |

| 5.4.3 Simulation avant des instructions . . . . .         | 113        |

| 5.5 CONCLUSION . . . . .                                  | 125        |

| <b>6 MODÈLES MÉMOIRE FAIBLES</b>                          | <b>127</b> |

| 6.1 INTRODUCTION . . . . .                                | 128        |

| 6.2 DÉFINITIONS . . . . .                                 | 130        |

| 6.2.1 Prolog et CHR . . . . .                             | 130        |

| 6.2.2 Langage considéré . . . . .                         | 137        |

| 6.2.3 Relations de base entre instructions . . . . .      | 138        |

| 6.3 MODÈLE GÉNÉRIQUE . . . . .                            | 140        |

| 6.3.1 Extraction de PO et des dépendances . . . . .       | 141        |

| 6.3.2 Extraction de CO et RF . . . . .                    | 142        |

| 6.3.3 Production de FR et IPO, atomicité de RMW . . . . . | 143        |

| 6.3.4 Dérivation des barrières . . . . .                  | 145        |

| 6.4 MODÈLES SPÉCIFIQUES . . . . .                         | 146        |

| 6.4.1 Détection de cycles . . . . .                       | 146        |

| 6.4.2 Le modèle SC . . . . .                              | 150        |

| 6.4.3 Relation SC par adresse . . . . .                   | 152        |

| 6.4.4 Les modèles TSO et PSO . . . . .                    | 153        |

| 6.5 JUSTIFICATION DE LA TERMINAISON . . . . .             | 157        |

|                      |                                                               |            |

|----------------------|---------------------------------------------------------------|------------|

| 6.5.1                | Génération des exécutions candidates . . . . .                | 157        |

| 6.5.2                | Relations dérivées par des règles CHR . . . . .               | 158        |

| 6.5.3                | Détection de cycles . . . . .                                 | 159        |

| 6.6                  | CORRECTION ET PERFORMANCES . . . . .                          | 161        |

| 6.6.1                | Suppression de contraintes . . . . .                          | 161        |

| 6.6.2                | Complexité de la génération des candidats . . . . .           | 162        |

| 6.6.3                | Tests empiriques de correction et performances . . . . .      | 165        |

| 6.7                  | CONCLUSION . . . . .                                          | 167        |

| <b>7</b>             | <b>CONCLUSION ET PERSPECTIVES</b>                             | <b>169</b> |

| 7.1                  | RAPPEL DES OBJECTIFS . . . . .                                | 169        |

| 7.2                  | BILAN DES TRAVAUX RÉALISÉS . . . . .                          | 170        |

| 7.3                  | PERSPECTIVES ENVISAGÉES . . . . .                             | 171        |

| 7.3.1                | CONC2SEQ et modèles mémoire faibles . . . . .                 | 172        |

| 7.3.2                | CONC2SEQ et les greffons de FRAMA-C . . . . .                 | 172        |

| 7.3.3                | Expérimentation sur des applications plus complexes . . . . . | 173        |

| 7.3.4                | Extension de la méthode aux fonctions récursives . . . . .    | 173        |

| <b>A</b>             | <b>GÉNÉRATION DES EXÉCUTIONS CANDIDATES : CODE PROLOG</b>     | <b>177</b> |

| A.1                  | EXTRACTION DE PO ET DES DÉPENDANCES . . . . .                 | 177        |

| A.2                  | PRÉDICATS PRÉALABLES À CO/FR . . . . .                        | 181        |

| A.3                  | EXTRACTION DE CO . . . . .                                    | 183        |

| A.4                  | EXTRACTION DE RF . . . . .                                    | 184        |

| <b>BIBLIOGRAPHIE</b> |                                                               | <b>185</b> |

## LISTE DES FIGURES

|     |                                                                                                                                           |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Fonction <code>swap</code> spécifiée en ACSL . . . . .                                                                                    | 24 |

| 3.1 | La fonction <code>set_entry</code> écrit la référence <code>new</code> dans la page <code>fn</code> à l'indice <code>idx</code> . . . . . | 36 |

| 3.2 | Simulation des exécutions concurrentes de <code>set_entry</code> de la figure 3.1, opérations atomiques . . . . .                         | 39 |

|      |                                                                                                                            |     |

|------|----------------------------------------------------------------------------------------------------------------------------|-----|

| 3.3  | Simulation des exécutions concurrentes de <code>set_entry</code> de la figure 3.1, entrelacements . . . . .                | 40  |

| 3.4  | Fonction logique <code>occ_a</code> pour le comptage d'occurrences dans les tableaux et axiomes . . . . .                  | 42  |

| 3.5  | Fonction logique <code>occ_m</code> pour compter les occurrences dans une plage de pages et axiomes . . . . .              | 43  |

| 3.6  | Invariant du compteur . . . . .                                                                                            | 43  |

| 3.7  | Prédicat définissant le lien entre le compteur de programme et le tableau <code>ref</code> . . . . .                       | 43  |

| 3.8  | Exemple de lemme ACSL pour compter dans deux sous-plages . . . . .                                                         | 44  |

| 4.1  | Exemple de politique multiples lecteurs/simple écrivain . . . . .                                                          | 58  |

| 4.2  | Spécification de <code>atomic_compare_exchange</code> . . . . .                                                            | 61  |

| 4.3  | Simulation du contexte d'exécution . . . . .                                                                               | 66  |

| 4.4  | Fonctions de simulation des étapes atomiques en lignes 22 et 32 de la figure 4.1 . . . . .                                 | 69  |

| 4.5  | Table des transformations . . . . .                                                                                        | 71  |

| 4.6  | Initialisation de l'appel à <code>read</code> dans la simulation . . . . .                                                 | 72  |

| 4.7  | Simulation des exécutions concurrentes par entrelacements . . . . .                                                        | 74  |

| 4.8  | Exemple d'usage de <code>thread_reduction</code> . . . . .                                                                 | 76  |

| 4.9  | Axiomatique pour <code>thread_reduction</code> , avec type <code>int</code> et fonction <code>sum</code> . . . . .         | 76  |

| 4.10 | Traduction de 4.8 à partir de 4.9 . . . . .                                                                                | 77  |

| 4.11 | Prédicats et lemmes pour <code>thread_reduction</code> , avec type <code>int</code> et fonction <code>sum</code> . . . . . | 78  |

| 5.1  | Sémantique opérationnelle des programmes séquentiels . . . . .                                                             | 91  |

| 5.2  | Sémantique opérationnelle des programmes parallèles . . . . .                                                              | 92  |

| 5.3  | Simulation de l'affectation . . . . .                                                                                      | 95  |

| 5.4  | Simulation de la lecture en mémoire . . . . .                                                                              | 95  |

| 5.5  | Simulation de l'écriture en mémoire . . . . .                                                                              | 96  |

| 5.6  | Simulation de la conditionnelle . . . . .                                                                                  | 96  |

| 5.7  | Simulation de la boucle . . . . .                                                                                          | 97  |

| 5.8  | Simulation d'appel . . . . .                                                                                               | 98  |

| 5.9  | Simulation de retour d'appel . . . . .                                                                                     | 98  |

| 5.10 | Simulation d'un bloc atomique . . . . .                                                                                    | 100 |

| 5.11 | Simulation d'une instruction . . . . .                                                                                     | 101 |

| 5.12 | Boucle d'entrelacements . . . . .                                                                                          | 102 |

|                                                                                                                                           |     |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.13 Relation de simulation . . . . .                                                                                                     | 108 |

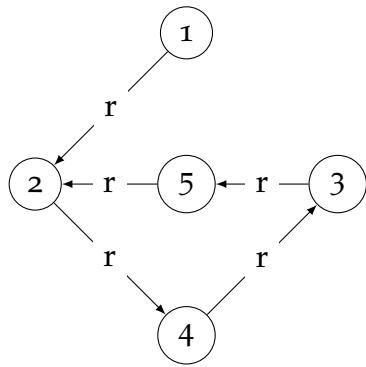

| 6.1 Exemple de programme concurrent. Relaxations : out-of-order, mémoire tampon . . . . .                                                 | 128 |

| 6.2 Contraintes en Constraint Handling Rules (CHR) . . . . .                                                                              | 132 |

| 6.3 Formes générales des règles CHR . . . . .                                                                                             | 133 |

| 6.4 Propagation et simplification par simpagation . . . . .                                                                               | 134 |

| 6.5 Traduction du programme de la figure 6.1 en Prolog . . . . .                                                                          | 137 |

| 6.6 Code avec dépendance d'adresse grâce aux registres nommés . . . . .                                                                   | 137 |

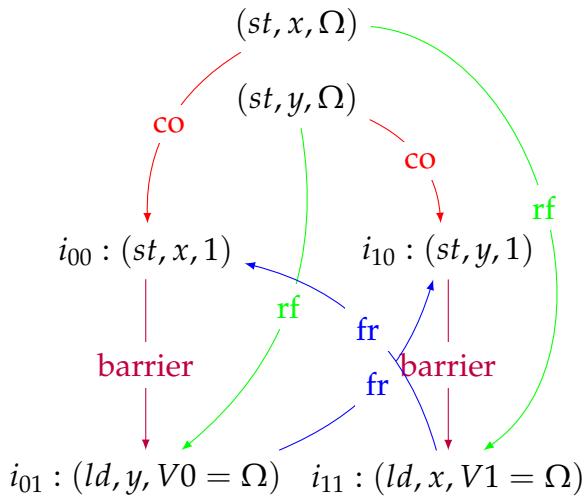

| 6.7 Exemple d'exécution du programme de la figure 6.1 . . . . .                                                                           | 138 |

| 6.8 Génération des exécutions candidates (generic_model.pl) . . . . .                                                                     | 140 |

| 6.9 Calcul de FR (generic_model.pl) . . . . .                                                                                             | 144 |

| 6.10 Calcul de IPO (generic_model.pl) . . . . .                                                                                           | 144 |

| 6.11 Règles de cohérence de RMW (generic_model.pl) . . . . .                                                                              | 145 |

| 6.12 Atomicité de RMW : scénarios interdits . . . . .                                                                                     | 145 |

| 6.13 Calcul des barrières (generic_model.pl) . . . . .                                                                                    | 146 |

| 6.14 Détection de cycles (cycle.pl) . . . . .                                                                                             | 147 |

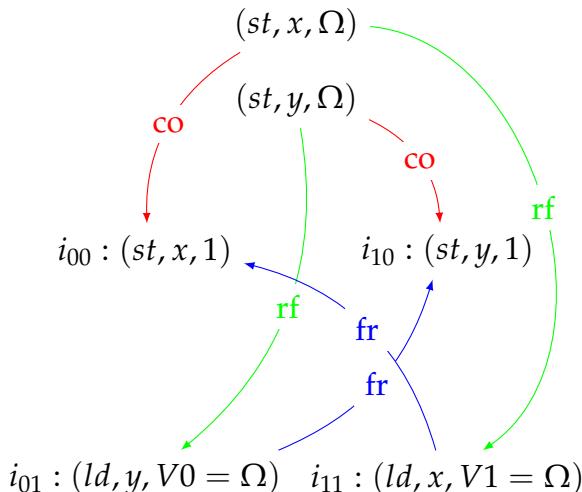

| 6.15 Exemple de graphe : configuration en « 6 » . . . . .                                                                                 | 149 |

| 6.16 Modèle SC (sc.pl) . . . . .                                                                                                          | 151 |

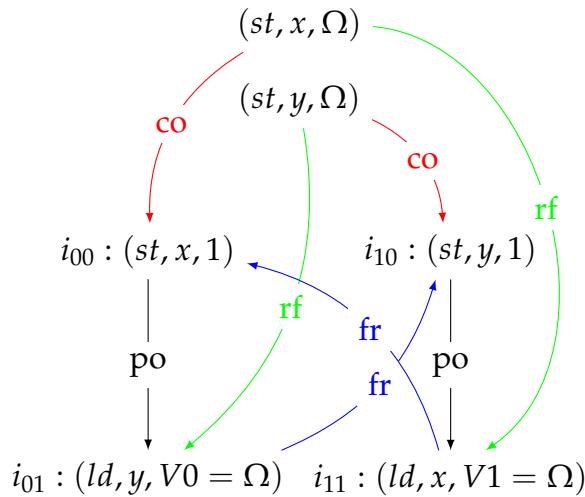

| 6.17 Exécution interdite par le modèle SC pour le programme de la figure 6.1 . . . . .                                                    | 152 |

| 6.18 Modèle SC par adresse (uniproc.pl) . . . . .                                                                                         | 153 |

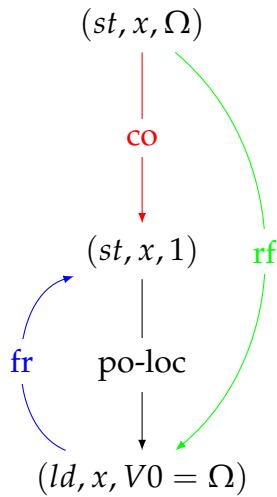

| 6.19 Exécution interdite par la relation sc_per_loc lors d'une lecture depuis une cellule précédemment écrite par le même fil d'exécution | 154 |

| 6.20 Modèle TSO (tso.pl) . . . . .                                                                                                        | 155 |

| 6.21 Modèle PSO (pso.pl) . . . . .                                                                                                        | 156 |

| 6.22 L'exécution interdite par le modèle SC pour le programme de la figure 6.1 est autorisé par TSO . . . . .                             | 156 |

| 6.23 Ajouts de barrières au programme de la figure 6.5 . . . . .                                                                          | 156 |

| 6.24 Exécution interdite par le modèle TSO pour le programme de la figure 6.23 grâce aux barrières . . . . .                              | 157 |

| 6.25 Deux manières de définir le sous-ensemble d'une relation . . . . .                                                                   | 162 |

| 6.26 Test de performances : passages de messages (code) . . . . .                                                                         | 166 |

| 6.27 Test de performances : passages de messages (résultats) . . . . .                                                                    | 166 |

| A.1 Enrichissement et extraction des instructions (generic_model.pl)                                                                      | 178 |

| A.2 Enrichissement et extraction des instructions (generic_model.pl)                                                                      | 179 |

| A.3 Extraction des contraintes PO (generic_model.pl) . . . . .                                                                            | 180 |

|                                                                       |     |

|-----------------------------------------------------------------------|-----|

| A.4 Extraction des dépendances (generic_model.pl) . . . . .           | 181 |

| A.5 Extraction des opérations par position mémoire (generic_model.pl) | 182 |

| A.6 Extraction des contraintes CO (generic_model.pl) . . . . .        | 183 |

| A.7 Extraction des contraintes RF (generic_model.pl) . . . . .        | 184 |

# INTRODUCTION

## SOMMAIRE

---

|     |                                     |    |

|-----|-------------------------------------|----|

| 1.1 | CORRECTION DES PROGRAMMES . . . . . | 3  |

| 1.2 | PREUVE DE PROGRAMMES . . . . .      | 5  |

| 1.3 | CONCURRENCE . . . . .               | 7  |

| 1.4 | PROPOSITION . . . . .               | 10 |

« Il n'y a pas de programme sans *bugs* ».

Cette phrase est souvent utilisée en commentaire d'actualité du monde informatique. Chaque jour, dans les logiciels que nous utilisons, de nouveaux *bugs* sont découverts, ces erreurs de programmation qui rendent parfois nos logiciels agaçants, en les fermant subitement à des moments inopportun ou en les rendant inutilisables, ou même inquiétants, en y exposant des failles de sécurité. Cela fournit une vision assez claire de ce que pensent les utilisateurs ou même les développeurs du monde de l'informatique. Malgré tous les efforts déployés pour faire des programmes corrects, il semble que cette tâche soit insurmontable, que nous soyons condamnés à avoir des programmes qui font des erreurs.

Pourtant nous connaissons beaucoup de programmes sans *bugs*. Cependant, acquérir la certitude qu'un programme est exempt de *bug* est difficile. Une des causes de cette difficulté est la taille des codes sources de nos logiciels. Aujourd'hui, le noyau de système d'exploitation Linux a dépassé les seize *millions* de lignes de code, une distribution complète reposant sur ce noyau est de l'ordre de 200 à 300 *millions* de lignes. Même un « simple » navigateur web est composé d'au moins une dizaine de *millions* de lignes. Dans de telles quantités de code, il est difficile de s'assurer qu'aucune fonction n'est mal utilisée ou qu'aucune faute de frappe n'a changé subtilement le comportement d'une ligne.

De plus en plus de techniques existent pour faciliter le développement et la validation de systèmes informatiques. Généralement en validation, plus la confiance apportée par une technique est élevée, plus il est difficile de l'appliquer

sur de grandes quantités de code. Par exemple, tester un programme donne une assurance plutôt faible mais est facile à appliquer, même sur de grandes quantités de code. Prouver un programme est difficile sur de grandes quantités de code, mais donne une grande confiance.

Ces dernières années, un nouveau facteur est venu s'ajouter aux difficultés que l'on rencontre lorsque l'on doit écrire du logiciel à grande échelle. Nos processeurs sont devenus « multi-cœurs ». Un processeur est maintenant composé de plusieurs unités de calcul qui peuvent, dans une certaine mesure, calculer indépendamment les unes des autres, tout en étant capables d'accéder à la même mémoire. Les développeurs ont donc commencé à écrire des programmes tirant parti de tels processeurs.

Cependant, nos processeurs peuvent accéder à la même mémoire, et de fait, plusieurs parties du programme s'exécutant en même temps peuvent accéder aux mêmes informations. Il en résulte que, si prises une à une ces parties peuvent sembler tout à fait correctes, leur interaction pourrait, elle, provoquer une erreur. Par exemple, si deux parties modifient des informations de manière incohérente l'une par rapport à l'autre.

Ce problème existait déjà avant la naissance des processeurs multi-cœurs, qui l'ont rendu plus répandu. Un processeur mono cœur suffit pour exécuter plusieurs programmes accédant à la même mémoire. Par exemple, nos systèmes d'exploitation sont depuis longtemps capables de faire fonctionner de multiples logiciels en leur donnant accès à un processeur chacun à leur tour, mais suffisamment vite, pour que l'on ait l'impression que tous ces programmes agissent en même temps.

Nous appelons « programmation concurrente », le paradigme de programmation dans lequel nous tenons compte du fait que dans un même programme, il existe plusieurs fils d'exécution, ou plusieurs processus, qui possèdent chacun leur propre mémoire, mais peuvent également accéder à une mémoire commune, par exemple pour communiquer. Du fait des difficultés de prendre en compte le déroulement et les effets de plusieurs processus exécutés en même temps, il est communément admis qu'il est plus difficile d'écrire, ou d'assurer la correction des programmes concurrents que des programmes séquentiels (ne comprenant qu'un seul programme dans son propre environnement). De ce fait, les techniques qui permettent le développement et la validation de programmes concurrents sont généralement plus difficiles à mettre en œuvre que celles dédiées aux programmes séquentiels.

Dans cette thèse, nous visons à fournir un moyen d'utiliser les techniques

de vérification dédiées aux programmes séquentiels, notamment la preuve de programmes, pour vérifier des programmes concurrents. Nous explorons ici la possibilité de transformer les programmes concurrents en programmes séquentiels équivalents, pour tirer parti des outils utilisés pour assurer le fonctionnement correct des programmes séquentiels. Nous présenterons plus en détails notre proposition en fin de chapitre. Dans un premier temps, nous allons rappeler la problématique de la validation et l'intérêt de la preuve pour l'effectuer. Cela nous permettra d'introduire quelques notations utilisées dans la suite de ce manuscrit.

## 1.1 CORRECTION DES PROGRAMMES

Nous voulons nous assurer que nos logiciels font ce que nous voulons d'eux. Donc dans un premier temps, nous devons être capables d'exprimer ce besoin.

Dans le développement de logiciels, cela se traduit généralement par la définition d'un cahier des charges. Celui-ci décrit, aussi clairement que possible, les besoins auxquels le logiciel va devoir répondre ainsi que les contraintes sous lesquelles il devra le faire. Ce sont, le plus souvent, des documents textuels, rédigés en langue naturelle, qui sont d'autant plus vastes et complexes que le système décrit l'est lui-même. Implémenter ou vérifier la correction d'un programme nécessite de comprendre correctement ces documents. Le fait que ces documents soient en langue naturelle introduit un premier risque, autant pour l'implémentation que pour la validation : les phrases peuvent être sujettes à l'interprétation et les personnes qui vont se succéder dans la création, la maintenance et la vérification de la correction d'une fonctionnalité n'auront peut-être pas la même interprétation.

Une fois la fonctionnalité implémentée, vient la deuxième étape qui est sa validation. Généralement, cette validation est effectuée par l'exécution de tests. Ils vont exécuter la fonctionnalité que l'on souhaite valider dans divers scénarios dont on connaît le résultat attendu. La fonctionnalité produira ou non ce résultat, validant ou non le test correspondant.

Par exemple, nous pouvons prendre un petit programme qui calcule la valeur absolue d'un entier :

```

1 int abs(int value) {

2     return (value < 0) ? -value : value ;

3 }

```

La spécification d'une telle fonctionnalité pourrait se résumer à : « *La fonction abs calcule la valeur absolue de la valeur qu'elle reçoit en paramètre. La valeur INT\_MIN est exclue de son champ d'application car sa valeur absolue n'est pas définie pour un entier de 32 bits* ».

Une suite de tests possible pour cette fonction pourrait simplement être :

| entrée    | Sortie  |

|-----------|---------|

| INT_MIN+1 | INT_MAX |

| -42       | 42      |

| -1        | 1       |

| 0         | 0       |

| 1         | 1       |

| 42        | 42      |

| INT_MAX   | INT_MAX |

où nous testons les valeurs calculées pour les cas aux limites : les bornes minimale et maximale de l'entier reçu, des valeurs proches de 0 (marquant les valeurs pour lesquelles la fonction doit changer de comportements), mais aussi pour des valeurs supplémentaires entre ces limites.

Cependant, une telle suite ne couvre pas tous les scénarios d'utilisation possibles. Nous pouvons régler le problème en testant exhaustivement la fonction. C'est-à-dire en essayant toutes les entrées comprises entre `INT_MIN+1` et `INT_MAX`.

Mais nous ne pouvons pas toujours être exhaustif. Par exemple, si nous voulons tester une fonction effectuant le tri d'un tableau d'entiers, il faudrait tester la fonction pour toutes les tailles de tableau entre 0 et  $2^{64} - 1$  et pour toutes les valeurs d'entiers pour chaque case de chaque tableau.

Généralement, l'ensemble des scénarios d'utilisation défini par le cahier des charges sera très grand, voire infini. Nous ne pouvons donc pas tous les tester. Notre campagne de tests ne pourra donc être qu'une validation partielle de ce qui est spécifié par le cahier des charges.

C'est là que les méthodes formelles entrent en jeu, nous donnant la possibilité de spécifier mathématiquement tous les comportements acceptables de notre programme, et nous donnant, la possibilité de vérifier que le code de notre implémentation assure effectivement que ces comportements sont respectés.

## 1.2 PREUVE DE PROGRAMMES

Comme pour d'autres méthodes de validation et vérification, l'objectif de la preuve de programmes est de déterminer si un programme répond à sa spécification. Seulement, comme il n'est généralement pas possible d'effectuer toutes les exécutions d'un programme pour examiner leur résultat, la preuve prend le parti de faire cette vérification sans exécuter le programme. En preuve, nous raisonnons à propos des propriétés des valeurs des variables du programme, en prenant en compte les effets que vont avoir les instructions sur elles.

Par exemple :

```

1 int a = rand() %10 ;

2 a += 1;

```

Après la première instruction, nous savons qu'une propriété de  $a$  est  $0 \leq a < 10$ . L'instruction suivante ajoute 1 à  $a$ , donc nous pouvons en déduire qu'après la deuxième instruction  $1 \leq a < 11$ , et ceci sans exécuter le programme pour toutes les valeurs possibles de  $a$ .

Pour chaque instruction possible dans un langage, nous pouvons définir comment elle fait évoluer la mémoire pendant l'exécution, et donc comment les propriétés respectées par les éléments de cette mémoire évoluent. Nous pouvons, de ce fait, créer des outils qui sont capables d'effectuer ce type de raisonnement. Nous y reviendrons plus précisément dans le chapitre 2.

Le greffon Wp est l'un des analyseurs de la plateforme d'analyse de programmes C Frama-C, que nous présenterons dans le chapitre 2. Il implémente un calcul de « plus faibles pré-conditions » (que nous présenterons également ultérieurement). Ce calcul fonctionne dans le sens inverse de l'exemple précédent. À savoir que nous allons, à partir de la *post-condition* voulue du programme (« après mon programme, la valeur renournée doit être la valeur absolue du nombre en entrée »), calculer les conditions en début de programme qui garantissent cette post-condition. Ce calcul est fait en remontant les instructions une à une dans le sens inverse du programme.

Par exemple, dans le programme précédent, si nous voulons qu'il termine avec la propriété  $1 \leq a < 11$ , que doit être la propriété de  $a$  avant l'exécution de  $a += 1$ ? Il faut que  $a$  respecte  $0 \leq a < 10$ .

Si la pré-condition donnée par l'utilisateur est au moins aussi forte que la condition nécessaire calculée, le programme est vérifié.

Pour vérifier notre fonction de calcul de la valeur absolue avec Frama-C et Wp, nous devons d'abord spécifier ce que l'on attend d'elle. Cela se fait par

l'ajout d'annotations en ACSL. Nous présenterons plus précisément ce langage de spécification dans le chapitre 2, nous précisons simplement que le mot clé `requires` introduit une pré-condition, et `ensures` une post-condition. Le mot clé `\result` correspond à la valeur de retour de la fonction, et l'opérateur `==>` à l'implication logique.

```

1 /*@

2  requires INT_MIN < value;

3  ensures value < 0 ==> \result == -value;

4  ensures value >= 0 ==> \result == value;

5 */

6 int abs(int value) {

7     return (value < 0) ? -value : value;

8 }

```

Ensuite, nous pouvons demander à FRAMA-C et WP d'effectuer la vérification, comprenant la recherche d'erreurs d'exécution potentielles, et les propriétés en question seront bien validées. La capture d'écran suivante illustre cette validation, les pastilles vertes montrent les propriétés assurées par la pré-condition. À côté de la pré-condition, nous pouvons voir un cercle bleu qui signifie qu'aucune vérification n'a été tentée. En effet, ces propriétés sont vérifiées par l'outil aux points d'appel de la fonction.

```

/*@ requires -2147483647-1 < value;

ensures \old(value) < 0 => \result = -\old(value);

ensures \old(value) ≥ 0 => \result = \old(value);

*/

int abs(int value)

{

int tmp;

if (value < 0) {

/*@ assert rte: signed_overflow: -2147483647 ≤ value; */

tmp = - value;

}

else {

tmp = value;

}

return tmp;

}

```

Les techniques de preuve permettent d'assurer que pour tout scénario d'exécution, le programme est conforme à sa spécification. Cependant comme nous n'exécutons pas le programme, nous construisons une abstraction des états du programme et celle-ci peut s'avérer imprécise. Cela peut rendre d'une part la

preuve difficile et d'autre part rendre l'identification de *bugs* complexe. Si la preuve ne réussit pas, le programme est-il faux ? La spécification est-elle insuffisante ? Ou mon outil est-il trop limité ?

Par exemple, si nous ne donnons pas la pré-condition indiquant que la valeur reçue par `abs` doit être supérieure à `INT_MIN`, l'assertion affirmant que l'opération `-value` ne déborde pas n'est pas validée. Au premier abord, il n'est pas facile de déterminer pourquoi, car la seule information obtenue est « la preuve ne passe pas ». Dans ce genre de cas, tester devient intéressant car cela permettra de trouver des cas qui sont effectivement des erreurs.

Dans la suite de cette thèse, nous nous intéresserons en priorité aux techniques de preuve de programmes puisque c'est le premier objectif que nous avons visé lorsque nous avons développé notre méthode d'analyse.

## 1.3 CONCURRENCE

Nous désirons effectuer la preuve de programmes concurrents. Par exemple, si nous avons un programme parallèle comme celui présenté ci-dessous, nous voulons lui appliquer des techniques de preuve. La syntaxe de la forme `{{{ i1 ||| i2 }}}}` exprime (dans ce programme en pseudo-C) « exécuter parallèlement `i1` et `i2` ».

```

1 int x = 0;

2 {{{ /*t1*/ x++; ||| /*t2*/ x++; }}}}

```

Dans un tel programme, une propriété que l'on pourrait attendre est que la valeur `x` après l'exécution est 2 : on a deux fils d'exécution, ajoutant chacun 1 à `x` qui vaut initialement 0.

En fait, si l'on suit la sémantique de ce programme, il expose un comportement indéterminé sous la forme d'un *data-race*. Commençons par réécrire le programme avec un grain plus fin. Lorsque l'on écrit `x++`, nous avons trois opérations : `x` est lire en mémoire, incrémentée, puis réécrite en mémoire.

```

1 int x = 0;

2 {{{

3     // t1

4     int y1 = x;

5     x = y1+1;

6     // t2

7     int y2 = x;

}}}

```

```

7     x = y2+1;

8 } }

```

Dans un tel programme, rien ne nous garantit par exemple que si la lecture de `x` dans `y1` est 0, la lecture de `x` dans `y2` est 1. Les deux programmes peuvent très bien lire 0 en même temps puis écrire 1 dans la mémoire chacun à leur tour, car rien n'ordonne ces instructions les unes par rapport aux autres.

De manière plus générale, un *data-race* apparaît lorsque deux instructions qui ne sont pas ordonnées l'une par rapport à l'autre, dont l'une au moins est une écriture, peuvent accéder à la même donnée en mémoire et produire ainsi une incertitude sur les valeurs manipulées. Cela rend le résultat des opérations imprévisible et on considère qu'un tel programme comprend une erreur d'exécution.

Il existe divers moyens d'assurer l'absence de *data-race* dans un programme ou de vérifier cette absence. Nous ne considérons pas ce problème dans cette thèse. Ici par exemple, un moyen simple de supprimer la situation de *data-race* est d'utiliser une fonction d'incrémentation atomique. En langage C, cette fonction s'appelle `atomic_fetch_add`, et garantit que les opérations de lecture, incrément, puis écriture sont effectuées dans un pas d'exécution indivisible (atomique). Donc l'une des opérations aura lieu avant l'autre, nous ne savons pas laquelle, mais la situation de *data-race* expliquée précédemment ne peut plus arriver. Pour simplifier la lecture, nous conservons l'écriture `x++`.

Pour prouver ce programme, la difficulté principale est d'amener d'un fil d'exécution à l'autre, l'information sur le travail effectué. Par exemple ici, il nous faut un moyen pour signifier à `t2` que `t1` peut avoir déjà réalisé son incrément de `x`, et inversement.

Dans la méthode d'Owicki-Gries [77] (que nous présenterons plus en détails dans le chapitre 2), cela passe par l'ajout de variables auxiliaires qui vont permettre d'exprimer comment l'état évolue dans un fil, en fonction de l'état des autres fils.

Dans cette nouvelle version du code, on ajoute des variables auxiliaires qui indiquent pour un fil donné s'il a effectué son instruction d'incrémentation. On considère que dans un fil, l'exécution de `x++` et la modification de la variable auxiliaire correspondante sont effectuées dans le même pas d'exécution (les variables auxiliaires ne sont ici présentes que d'un point de vue logique, elles n'existent pas réellement dans le programme).

```

1 int x = 0;

2 /* done_1 = 0 ; done_2 = 0 ; */

3 {{ /*t1*/

4     x++; /*done_1 = 1*/

5 ||| /*t2*/

6     x++; /*done_2 = 1*/

7 }}

```

Pour prouver ce programme, l'idée de la méthode d'Owicki-Gries est alors d'exprimer la pré-condition de chaque fil en fonction de l'état des variables auxiliaires. Par exemple, pour  $t_1$  :

$$\{ \text{done\_1} = 0 \wedge (\text{done\_2} = 0 \Rightarrow x = 0) \wedge (\text{done\_2} = 1 \Rightarrow x = 1) \}$$

Nous pouvons alors calculer qu'après l'exécution de son incrément, la propriété est :

$$\{ \text{done\_1} = 1 \wedge (\text{done\_2} = 0 \Rightarrow x = 1) \wedge (\text{done\_2} = 1 \Rightarrow x = 2) \}$$

Nous pouvons appliquer un raisonnement similaire pour le fil d'exécution  $t_2$  et par la connaissance générée qu'à la fois `done_1` et `done_2` valent 1, déduire que `x` vaut 2.

La méthode d'Owicki-Gries fournit aussi des règles supplémentaires pour assurer que les variables auxiliaires ne modifient pas le comportement du programme. Nous n'expliquons pas ce point ici.

Il existe diverses méthodes pour raisonner à propos des programmes concurrents. Celles-ci ont généralement été conçues avec cette optique particulière et y sont donc dédiées. Il est par conséquent difficile d'adapter des outils développés pour les programmes séquentiels en se basant sur ces méthodes. Nous pouvons donc nous demander comment tirer parti des outils conçus pour l'analyse de programmes séquentiels afin d'analyser des programmes concurrents.

Dans cette thèse, nous nous focalisons sur les programmes concurrents exécutés selon un modèle particulier d'accès à la mémoire : le modèle *séquentiellement consistant*. Dans ce modèle, nous considérons que les exécutions d'un programme peuvent être vues comme les entrelacements des instructions de ses différents fils d'exécution.

Pour notre programme d'exemple, nous aurions :

- $t_1:x++$  puis  $t_2:x++$ ;

- $t_2:x++$  puis  $t_1:x++$ .

Dans un cadre plus général, celui des modèles de nos architectures matérielles par exemple, les entrelacements ne sont pas les seules exécutions autorisées. Leurs modèles mémoire, dits « faibles », permettent d'autres exécutions qui ne correspondent pas à des entrelacements. Cependant, une propriété importante que la majorité d'entre eux respecte, est que si les exécutions d'un programme selon le modèle mémoire séquentiellement consistant ne contiennent pas de *data-race*, alors l'ensemble de ses exécutions a un comportement séquentiellement consistant. Une manière possible de s'assurer que l'on peut traiter un programme selon cette hypothèse est donc de vérifier l'absence de *data-race*.

Dans le cadre du modèle mémoire séquentiellement consistant, nous pouvons voir les exécutions d'un programme concurrent comme un ensemble d'exécutions séquentielles où les instructions de chaque fil d'exécution sont entrelacées. Une approche est donc de construire ces exécutions afin de simuler le fonctionnement du programme concurrent. Il convient en revanche de ne pas construire explicitement chacune de ces exécutions (une nouvelle fois, nous ne pouvons nous permettre d'être exhaustif), mais de produire un programme dont on a l'assurance que toutes ses exécutions sont équivalentes à celles du programme concurrent simulé.

## 1.4 PROPOSITION

Dans cette thèse, nous proposons de traiter les programmes concurrents en produisant une simulation de leurs exécutions concurrentes. Le code de cette simulation pourra être analysé statiquement ou dynamiquement.

Le principe de cette simulation consiste à faire l'hypothèse d'un nombre de fils d'exécution constant mais arbitrairement grand possédant chacun un identifiant. Le contexte d'exécution de chaque fil est modélisé de telle manière que chaque variable locale est simulée par l'usage d'un tableau associant à chaque identifiant de fil la valeur de la variable. Une autre zone mémoire permet de sauver pour chaque fil d'exécution sa position actuelle dans l'exécution du programme, c'est-à-dire son compteur de point de programme. Chaque action atomique réalisée par le programme est ensuite simulée par une fonction qui effectue la même opération mais où chaque accès est effectué dans les tableaux simulants et à l'indice correspondant au fil d'exécution actuellement exécuté. L'ensemble des fonctions simulantes est ensuite exécuté par une boucle les entrelaçant de manière non déterministe. Nous supposons donc que les programmes

ont une sémantique d’entrelacements et qu’ils sont exécutés selon le modèle mémoire séquentiellement consistant.

Cette méthode est implémentée par un greffon de la plateforme FRAMA-C appelé CONC2SEQ. Cela a deux implications pour la méthode. D’une part, le programme d’origine est spécifié par l’utilisateur. Comme nous le modifions, les spécifications en question sont adaptées par le greffon, conformément à la transformation effectuée sur le code, afin de pouvoir les prouver sur le programme simulant. D’un point de vue technique, nous fournissons également de nouvelles primitives dans le langage ACSL et certaines facilités pour pouvoir parler plus aisément des propriétés de programmes concurrents.

L’autre implication de l’application de la méthode au langage C est due à la norme du langage. En effet, celle-ci impose, pour qu’un programme soit correct, qu’il soit dépourvu de *data-race* [53, Sec. 5.1.2.4]. Comme expliqué dans la section 2.4, une telle propriété nous garantit pour les modèles mémoires courants que le programme n’exhibe que des comportements séquentiellement constants, satisfaisant notre hypothèse. L’absence de *data-race* reste encore à prouver mais nous pouvons déléguer cette partie du travail au greffon MTHREAD de FRAMA-C (que nous décrivons succinctement dans le chapitre 2), et voulons fournir un moyen de prouver des propriétés fonctionnelles à propos des programmes concurrents.

Nous nous intéressons néanmoins au fonctionnement des programmes selon les modèles mémoire faibles à travers le prototypage d’un outil d’analyse des programmes sous un modèle mémoire faible. Partant du constat que les modèles mémoires sont généralement exprimés axiomatiquement, et contraignent les comportements autorisés par le modèle, nous utilisons les langages Prolog et CHR pour modéliser et résoudre ces contraintes sur un langage basique et déterminer les exécutions autorisées par un modèle mémoire donné. Cela nous permet entre autres de bénéficier de l’usage d’un moteur de résolution tel que ceux utilisés pour Prolog par rapport à une implémentation directe d’un moteur de résolution dédié aux modèles mémoire faibles.

La suite de ce manuscrit s’articule comme suit. Nous présentons dans le chapitre 2, une vue d’ensemble des méthodes et outils existants pour l’analyse de programmes. Dans le chapitre 3 nous présentons l’étude de cas pour laquelle nous avons appliqué notre méthode d’analyse par simulation et les résultats de l’étude effectuée, notamment les besoins identifiés pour son automatisation. La méthode automatisée est présentée dans le chapitre 4, où nous énonçons les fonctionnalités du greffon écrit pour FRAMA-C et la manière dont elles sont

implémentées. Ensuite, dans le chapitre 5 nous montrons la correction de notre méthode, en particulier l'équivalence sémantique entre le programme concurrent en entrée et le programme séquentiel simulant en sortie. Le chapitre 6 présente notre prototype de solveur pour les modèles mémoire faibles, ses fonctionnalités, sa correction et son évaluation. Finalement, le chapitre 7 conclut sur notre travail et présente les perspectives envisagées.

Des versions préliminaires des résultats présentés dans ce mémoire ont été présentés et publiés dans les colloques suivants :

- A. Blanchard, N. Kosmatov, M. Lemerre, and F. Loulergue. *A Case Study on Formal Verification of the Anaxagoros Hypervisor Paging System with Frama-C*. FMICS, Formal Methods for Industrial Critical Software, Springer 2015 [18];

- A. Blanchard, N. Kosmatov, M. Lemerre, and F. Loulergue. CONC2SEQ: *A FRAMA-C Plugin for Verification of Parallel Compositions of C Programs*. SCAM, Source Code Analysis and Manipulation, 2016 [19];

- A. Blanchard, N. Kosmatov, and F. Loulergue. *A CHR-Based Solver for Weak Memory Behaviors*. CSTVA, Constraint Solvers in Testing, Verification, and Analysis, co-located with ISSTA, 2016 [20].

# ÉTAT DE L'ART

2

## SOMMAIRE

---

|       |                                                        |    |

|-------|--------------------------------------------------------|----|

| 2.1   | MÉTHODES DE VÉRIFICATION                               | 14 |

| 2.1.1 | Test                                                   | 14 |

| 2.1.2 | Interprétation abstraite                               | 15 |

| 2.1.3 | Model-Checking                                         | 15 |

| 2.1.4 | Logiques de Hoare                                      | 16 |

| 2.1.5 | Logique de séparation                                  | 17 |

| 2.2   | PROGRAMMES CONCURRENTS                                 | 18 |

| 2.2.1 | Méthode de Hoare                                       | 19 |

| 2.2.2 | Méthode d'Owicki-Gries                                 | 20 |

| 2.2.3 | Rely-Guarantee                                         | 21 |

| 2.2.4 | Logique de séparation concurrente                      | 22 |

| 2.2.5 | Combinaison de Rely-Guarantee et logique de séparation | 22 |

| 2.3   | OUTILS D'ANALYSE DE CODE C                             | 23 |

| 2.3.1 | FRAMA-C                                                | 23 |

| 2.3.2 | VCC                                                    | 25 |

| 2.3.3 | VERIFAST                                               | 26 |

| 2.4   | MODÈLES MÉMOIRE FAIBLES                                | 27 |

| 2.4.1 | Formalisations                                         | 27 |

| 2.4.2 | Identification d'exécutions                            | 28 |

| 2.4.3 | Logiques                                               | 29 |

| 2.4.4 | Retrouver le modèle séquentiellement consistant        | 29 |

---

Dans ce chapitre, nous présentons un ensemble de travaux de la littérature à propos de l'analyse de programmes. Certains points déjà évoqués dans le chapitre 1 sont de nouveaux abordés pour les replacer par rapport aux autres méthodes et logiciels mentionnés ici. Nous donnons également un peu plus de détails à leur sujet.

Dans un premier temps, nous nous intéressons aux programmes séquentiels (dans la section 2.1), pour lesquels nous présentons diverses méthodes d'analyse et logiques de programmes. Pour ces dernières, nous présentons, dans la section 2.2, les logiques qui en ont été dérivées pour le traitement de programmes concurrents. Dans la section 2.3, nous présentons plusieurs outils d'analyse de programmes écrits en langage C, dont FRAMA-C, la plateforme pour laquelle nous avons implémenté notre méthode. Finalement, la section 2.4 répertorie divers travaux à propos de la prise en compte des modèles mémoire des processeurs lors de l'analyse de programmes concurrents.

## 2.1 MÉTHODES DE VÉRIFICATION

### 2.1.1 Test

Pour vérifier le bon fonctionnement des programmes, la méthode la plus employée en industrie est le test. C'est une analyse *dynamique*, elle nécessite d'exécuter le programme sur un ensemble d'entrées afin d'assurer que les résultats produits sont conformes. La spécification du programme en vue de sa validation prend alors la forme d'une association des entrées testées vers les sorties attendues du programme. Ces tests peuvent être réalisés sur l'ensemble du programme (souvent dénommé « test d'intégration et de validation ») ou sur des fonctionnalités isolées (test unitaire).

L'avantage du test est principalement sa précision. Le résultat que nous obtenons est très précisément celui produit par le programme puisque nous l'avons obtenu en l'exécutant. Donc si notre analyse nous indique qu'un résultat n'est pas conforme à l'attente, le verdict est sûr. En revanche, le test n'est pas complet, nous ne pouvons essayer qu'un nombre limité d'entrées pour un programme donné, et les entrées réelles peuvent être en nombre très grand, ou infini. Il en résulte que si nos tests ne trouvent pas de bugs, à moins que nous ayons testé exhaustivement toutes les entrées possibles du programme, nous n'avons pas de certitude qu'il ne contient aucun bug.

Il existe diverses métriques pour déterminer la qualité de la couverture d'un programme par les tests [9]. Celles-ci peuvent être exploitées, en combinaison avec des analyses statiques, pour générer automatiquement un grand nombre de tests susceptibles d'améliorer la qualité de la couverture et donc la confiance que l'on peut avoir dans le programme. Par opposition aux analyses dynamiques,

les analyses statiques sont effectuées sans exécuter le code, nous en présentons plusieurs par la suite.

Tester permet d'éliminer, avec des coûts raisonnables, une bonne quantité de bugs. En l'occurrence, cela permet de montrer, sur l'ensemble des tests exécutés, l'absence d'un certain nombre de comportements identifiés comme problématiques, ou la présence de comportements identifiés comme voulus, mais pas pour l'ensemble des entrées et des comportements définis par la spécification générale. Pour cela, il est nécessaire de se tourner vers les méthodes formelles.

### 2.1.2 Interprétation abstraite

L'interprétation abstraite [36] est une technique d'analyse *statique* [72]. Contrairement au test, le programme n'est pas exécuté pour déterminer sa correction. On raisonne sur l'ensemble des comportements qui pourraient apparaître pendant l'exécution d'un programme afin de déterminer si ceux-ci sont effectivement contenus dans les comportements acceptables. Ces analyses sont en général indécidables [62] et reposent sur une approximation des états possibles d'un programme. Ces techniques peuvent donc être complètes (à condition que les approximations le permettent) mais sont imprécises, du fait des approximations.

Dans le cas de l'interprétation abstraite, l'approximation repose sur la théorie des treillis et le calcul de point fixe. D'une certaine manière, on analyse le comportement sur toutes les entrées possibles sans exécuter les instructions pour chacune d'entre elles. Le principe est de résoudre un ensemble d'équations déterminées à partir du programme et représentant sa sémantique. Les limites de cette méthode vont donc se trouver dans la capacité de l'outil à résoudre ces équations. S'il n'existe pas de procédure de décision automatique pour la résolution, les résultats restent très imprécis.

### 2.1.3 Model-Checking

La vérification de modèle (*model checking*) [28, 87] n'est pas à proprement parler une technique de vérification de code mais plutôt de systèmes (informatiques ou électroniques), représentés par un modèle. Cela peut par exemple concerner des protocoles ou des circuits de transistors.

Les propriétés du système sont généralement exprimées en utilisant des logiques temporelles. Le système est modélisé sous la forme d'un graphe états/-transitions à partir duquel on vérifie les propriétés voulues de manière automa-

tique. Concrètement, s'il existe un chemin dans le graphe qui ne respecte pas la propriété énoncée, alors le système contient une erreur. Il faut ensuite analyser cette erreur afin de déterminer si elle est due à la représentation du système par le modèle, ou si le système est effectivement fautif.

La méthode étant automatique, elle est facile à mettre en place pour un utilisateur (modulo l'expertise nécessaire pour la modélisation et l'analyse des erreurs). En revanche, les états atteignables d'un programme peuvent être très nombreux suivant le système vérifié. Il est possible de limiter l'explosion combinatoire en représentant les états de manière symbolique et non concrète. Dans le cas des programmes, le nombre d'états pouvant être vraiment colossal, ces représentations peuvent ne pas être suffisantes pour permettre la vérification. C'est notamment le cas quand le nombre d'états est infini, dans cette situation, des méthodes d'abstractions sont utilisées pour construire un modèle approximatif du système vérifié n'utilisant qu'un nombre fini d'états.

Ce type d'analyse est par exemple implémenté par les *model-checkers* SPIN [51] ou encore CUBICLE [34].

#### 2.1.4 Logiques de Hoare

Les logiques de Hoare [49] sont des logiques qui permettent de raisonner sur les programmes et leurs propriétés. Les triplets de Hoare, de la forme  $\{P\} c \{Q\}$  où  $P$  et  $Q$  sont des assertions logiques et  $c$  une séquence d'instructions, nous indiquent que depuis un état où le programme respecte la propriété  $P$ , la séquence d'instructions  $c$  nous amène dans un nouvel état où  $Q$  est respectée.

En logique de Hoare, il est possible de raisonner en terme de correction totale ou partielle. En correction totale, le triplet signifie que depuis un état qui respecte la pré-condition  $P$ , la séquence d'instructions  $c$  termine et atteint un nouvel état où  $Q$ , la post-condition, est respectée. En correction partielle nous ne considérons pas la preuve de terminaison, la signification est alors que depuis un état respectant  $P$ , si la séquence d'instruction  $c$  termine, alors l'état du système après exécution respecte  $Q$ .

Les logiques de Hoare reposent sur des systèmes d'inférence sur les triplets précédemment cités. Chaque instruction du programme, et les compositions successives de ces instructions, donnent lieu à un triplet dans l'arbre de dérivation. Il est donc souhaitable que cette inférence soit automatisée au maximum. C'est notamment l'objectif du calcul de plus faible pré-conditions [41], qui définit comment, à partir d'une post-condition donnée et d'un programme, on peut calculer

la pré-condition la plus faible nécessaire pour avoir un triplet valide. Ce calcul se fait par transformations successives du prédicat d'origine. Pour certaines instructions, ce calcul n'est cependant pas automatisable. C'est notamment le cas des boucles pour lesquelles il faudra renseigner les invariants que celles-ci doivent respecter.

Les outils automatiques utilisant cette méthode combinent généralement deux phases : un premier outil, le générateur d'obligations de preuve (*verification condition generator*, VCGen) reçoit en entrée le programme et sa spécification, à partir de ces éléments, il produit l'arbre de dérivation correspondant au plus faible pré-condition, avec aux feuilles les formules devant être vérifiées pour garantir la validité du programme : les obligations de preuves. Ces obligations de preuves sont ensuite déchargées par l'usage de prouveurs automatiques (solveurs SMT par exemple) ou interactifs (comme les assistants de preuve Coq [91] ou IsABELLE/HOL [74]) indépendants du langage d'entrée.

Les outils basés sur ce type de fonctionnement se montrent très efficaces lorsque les obligations de preuve peuvent être déchargés par les solveurs automatiques. Lorsque ce n'est pas le cas, il est nécessaire d'intervenir manuellement. Dans le cas des solveurs automatiques, il est possible de les guider par l'ajout d'assertions intermédiaires dans le code source ou des lemmes supplémentaires dans la base de connaissances, mais cela nécessite une certaine expertise des outils pour déterminer les raisons qui font que la preuve ne passe pas. Il est également possible de réaliser la preuve par l'usage de prouveurs interactifs. Le problème est alors que les obligations de preuve que produisent les générateurs sont souvent complexes à lire, en raison de trop fortes ou trop faibles simplifications effectuées par les heuristiques du générateur d'obligations, ainsi qu'à l'encodage des sémantiques pour les prouveurs cibles.

L'outil et le langage WHY3 [43] permettent par exemple de produire ce calcul de plus faible pré-conditions à partir d'un programme. Les obligations générées peuvent ensuite être déchargées par exemple par ALT-ERGO [33], CVC3 [13] ou encore CVC4 [14], que nous utilisons, dans le présent travail, pour décharger les obligations générées pour les programmes que nous analysons.

### 2.1.5 Logique de séparation

Les logiques de Hoare originelles permettent de raisonner sur les programmes mais sont rapidement limitées lorsque l'on souhaite raisonner sur des programmes qui manipulent des pointeurs. Dans ce type de cas, il est nécessaire

d'ajouter une couche supplémentaire de raisonnement pour expliciter le comportement de la mémoire, notamment en ce qui concerne les notions de partage de données et leur séparation spatiale. Or, une grande quantité de langages de programmation réels ont besoin des ressources dans le tas.

La logique de séparation [83] définit un moyen de raisonner à propos des programmes agissant sur le tas (elle permet notamment l'arithmétique de pointeurs). Le langage de base considéré par Hoare est enrichi avec des primitives concernant l'allocation, la désallocation et l'accès à des ressources du tas. Les triplets correspondant à cette logique sont définis pour chaque commande pour le raisonnement avant et arrière.

Le principal intérêt de la logique de séparation repose dans l'ajout de deux opérateurs à la logique du premier ordre usuel, à savoir la « *separating conjunction* » ( $P * Q$ ) et la « *separating implication* » ( $P -* Q$ ). La première signifie que  $P$  et  $Q$  sont des propriétés qui concernent des parties disjointes du tas ; la seconde indique que si l'on étend le tas avec une partie disjointe satisfaisant  $P$ , le tas résultant satisfait  $Q$ .

Selon Reynolds, l'ensemble des règles en raisonnement arrière fournit un calcul de plus faible pré-conditions complet [54]. Du fait de la présence des assertions à propos du tas, certaines règles d'inférence de la logique de Hoare sont invalides par défaut et ne peuvent donc être utilisées qu'en prouvant la pureté des assertions, c'est-à-dire en prouvant l'absence de propriétés à propos du tas.

Si les règles d'inférence de la logique de séparation peuvent effectivement être appliquées de manière automatique, la satisfiabilité de ces formules est un sujet encore complexe. Les techniques existantes traitent des sous-ensembles de la logique, soit en les transformant pour les rendre compréhensibles par des solveurs SMT standards [79, 82], soit par des algorithmes dédiés [24]. La logique de séparation est donc encore peu utilisée dans les outils d'analyse de programmes réalistes ou alors nécessite une instrumentation assez forte du code.

## 2.2 PROGRAMMES CONCURRENTS

Les programmes concurrents sont des programmes qui sont composés de plusieurs programmes s'exécutant simultanément (fils d'exécution ou *threads*) et pouvant accéder à des ressources partagées entre eux.

De tels programmes sont plus difficiles à analyser que les programmes séquentiels. Dans un programme séquentiel, une des difficultés les plus importantes apparaît lorsque nous sommes en présence d'*aliasing*, c'est-à-dire dans une situation où plusieurs variables d'un programme nous permettent un accès potentiel aux mêmes ressources. Il est alors plus difficile de déterminer comment évolue la ressource en question et donc ce que l'on peut lire depuis les différents points d'accès. Traiter de tels programme est l'une des motivations de la logique de séparation.

Dans un programme concurrent, nous faisons face au même problème en pire : non seulement nous sommes en présence d'*aliasing*, mais en plus les accès aux ressources partagées peuvent être effectués depuis plusieurs fils simultanément. En réalité, un ensemble d'opérations en mémoire (par exemple une lecture et une écriture) ne peuvent pas être effectuées simultanément pour une position en mémoire donnée au niveau matériel. Les requêtes de lecture ou d'écriture seront donc effectuées dans un certain ordre que nous sommes généralement incapables de déterminer de manière sûre. Cette situation est appelée *data-race*. Si deux actions dont au moins une écriture sont effectuées « en même temps » à une position mémoire donnée, nous ne pouvons pas prévoir le résultat des lectures pour une écriture et des lectures (on ne sait pas si l'écriture a effectivement été faite avant une lecture), ou la valeur désormais présente en mémoire si plusieurs écritures sont mises en jeu car on ne sait pas dans quel ordre elles seront exécutées.

Même en l'absence de *data-race*, assurer et vérifier la correction de propriétés fonctionnelles est une tâche complexe, l'ensemble des comportements possibles du programme explosant rapidement du fait des exécutions simultanées des différents fils d'exécution. Dans cette section, nous nous intéressons aux méthodes existantes pour prouver la correction de tels programmes.

Les techniques que nous présentons dans cette section supposent un modèle mémoire séquentiellement consistant tel que présenté dans [61], c'est-à-dire un modèle où les exécutions d'un programme concurrent peuvent se résumer aux entrelacements des instructions de chacun des fils d'exécution. Dans la section 2.4, nous nous pencherons sur les limites de cette hypothèse.

### 2.2.1 Méthode de Hoare

Un des travaux précurseurs en preuve de programmes parallèles est décrit par Hoare dans [48, 50]. Il s'agit une nouvelle fois d'une définition axiomatique

des comportements des programmes, mais concurrents cette fois. Les idées principales mises en avant sont : le besoin d'un langage de haut niveau pour la description abstraite de programmes parallèles et celui de s'abstraire des questions de temporalité pour assurer le bon fonctionnement de tels programmes. Si la première idée n'élimine pas le besoin d'un moyen de raisonner à plus bas niveau, ne serait-ce que pour implémenter les mécanismes proposés par un langage de plus haut niveau, la seconde est fondamentale car la diversité du matériel et des situations qui peuvent survenir pendant l'exécution du programme parallèle rendent la prédiction de l'ordre exact des événements impossible dans le cas général. Ce problème est donc abstrait dans toutes les logiques que nous présentons dans cette partie.

La logique définie par Hoare pour les programmes concurrents suit l'idée de [40], à savoir que les différents fils d'exécution d'un programme concurrent devraient s'exécuter au maximum indépendamment excepté en de rares points de synchronisation. Elle définit par conséquent des règles permettant de séparer les raisonnements sur les fils en leur attribuant chacun les ressources dont ils ont l'accès exclusif (à noter que l'on hérite quand même des problèmes déjà présents en logique de Hoare standard lorsque nous sommes en présence d'*aliasing*, voir section 2.2.4), et des règles permettant d'exprimer les moments de synchronisation, desquelles on évacue les problèmes de temporalité par la notion de ressources à accès exclusif. La syntaxe fournie est de la forme : `with resource r do c. c` pouvant être une suite d'instructions et `r` ne pouvant être acquise que par un seul fil d'exécution à la fois, nous sommes sûrs que deux fils ne peuvent pas exécuter la séquence d'instruction `c` en même temps. Une telle séquence est appelée *section critique*.

### 2.2.2 Méthode d'Owicki-Gries

La méthode d'Owicki-Gries [77] complète la logique de Hoare concurrente. Elle ajoute la notion d'invariant de ressource qui va permettre de vérifier des informations globales à propos du système lors de l'exécution de sections critiques. Ces invariants ne peuvent être (temporairement) violés que pendant l'exécution d'une section critique, il faut donc vérifier qu'aucune autre opération n'en a le pouvoir et que les sections restituent bien ces invariants (à noter qu'en dehors des sections, on ne peut pas supposer ces invariants puisqu'un autre fil peut être en train de le manipuler). Elle définit également la notion de variable auxiliaire qui pourrait aujourd'hui être vue comme la notion de variable « fantôme »,

c'est-à-dire des variables qui peuvent être assignées mais jamais lues par le programme, seulement du côté de la logique.

Par la combinaison de ces deux notions, il est possible de prouver des propriétés plus complexes à propos des programmes qu'en logique de Hoare concurrente, notamment lorsque celles-ci mettent en jeu la combinaison des opérations réalisées par chacun des fils d'exécution. En revanche, vérifier que les interférences entre ceux-ci n'entrent pas en conflit est coûteux et peu modulaire car cela nécessite de comparer les arbres de preuve des différents fils après la preuve de chacun d'eux, ce qui peut invalider la totalité du travail de vérification en fin de processus de preuve. Un exemple d'utilisation de cette méthode peut être trouvé dans le chapitre 1.

Cette méthode est par exemple implémentée en ISABELLE/HOL [73]. Et elle a été utilisée avec succès sur des problèmes de la vie réelle comme par exemple de la vérification de système d'exploitation [10].

### 2.2.3 Rely-Guarantee

Comme mentionné précédemment, la méthode d'Owicki-Gries possède le défaut de ne pas être suffisamment modulaire, notamment en ce qui concerne les propriétés de non-interférence. Pour pallier à ces difficultés, dans [56], Jones présente la *Rely-Guarantee*, une méthode permettant de définir précisément les interférences autorisées pour les fils d'exécutions. Elle est par exemple implémentée en ISABELLE/HOL [81].

Les « Rely »-conditions nous définissent comment l'environnement est susceptible de changer entre deux états du programme. Inversement, les « Guarantee »-conditions énoncent les interférences qu'un fil d'exécution est autorisé à générer entre deux états successifs du programme. Ces conditions sont donc des ensembles d'actions  $P \rightsquigarrow Q$  où  $P$  est une assertion à propos de l'état de départ et  $Q$  à propos de l'état d'arrivée. Les « Rely/Guarantee »-conditions sont définies au niveau global, elles doivent être réflexives (pour permettre à l'environnement de ne pas évoluer) et transitives (pour autoriser une série de changements) [56, Sec 3.1].

Nous pouvons par exemple exprimer qu'une variable croît de manière monotone d'un état à l'autre par la « Guarantee » condition :  $\forall x.t = x \rightsquigarrow x \leq t'$ . Où  $t'$  est la valeur de la variable  $t$  dans l'état qui suit. Cette relation entre les états est bien réflexive et transitive.

Une faiblesse de cette approche est que ces interférences sont définies globa-

lement. Elles doivent donc être vérifiées pour chaque modification de l'état du programme même si l'on sait trivialement que l'opération ne peut pas générer d'interférences dans un autre fil d'exécution.

### 2.2.4 Logique de séparation concurrente

Nous avons mentionné dans la section 2.2.1 que la logique décrite hérite des mêmes problèmes que la logique de Hoare en ce qui concerne la présence d'alias, ou encore d'exclusion non-structurée (dans le cas général) comme les sémaphores, la méthode Owicky-Gries héritant des mêmes limitations. Le but de la logique de séparation concurrente [75] est d'adapter la méthode d'Owicki-Gries en utilisant la logique de séparation.

L'isolation des ressources et l'absence de partage (quand c'est nécessaire) sont assurées par l'usage de la conjonction de séparation. Par exemple, nous pouvons imaginer un programme qui commence par allouer un tas tel que sur deux parties disjointes  $p$  et  $q$ , les propriétés  $P$  et  $Q$  sont respectées. Nous avons alors  $P * Q$ . Ensuite, ce programme lance un fil d'exécution en lui transmettant un accès à  $p$  et va, de son côté, manipuler le tas  $q$  tout en assurant qu'il ne modifiera pas  $p$ . Après le lancement du fil, le programme principal n'est plus associé qu'à la propriété  $Q$  et le fil d'exécution à la propriété  $P$ .

De cette manière, en tout point de programme, on peut connaître quelle partie du tas appartient à quel fil d'exécution (et par conséquent ce qu'il a le droit de modifier). Les invariants de ressources doivent néanmoins être des prédictats précis, à savoir qu'il ne peut exister qu'au plus un sous-tas du tas global tel que l'invariant formulé est vrai. Sinon, le transfert de ressource en entrée de bloc n'est plus déterministe et peut mener à des incohérences.

Contrairement à la *rely-guarantee*, cette méthode ne définit pas les interférences sur des états successifs. Elle exploite le même concept de section critique avec ressource que dans la logique de Hoare et son extension avec l'invariant de ressource apporté par la méthode d'Owicki-Gries. Comme dans cette dernière, exprimer les propriétés, souvent relationnelles, qu'impliquent les interférences nécessite de nombreuses variables auxiliaires qui peuvent complexifier la preuve.

### 2.2.5 Combinaison de Rely-Guarantee et logique de séparation

Le travail présenté par [94] vise à concilier les forces de la *rely-guarantee* et de la logique de séparation concurrente, à savoir conserver la modularité de la

preuve et la séparation des ressources tout en autorisant une expression précise des interférences dans les programmes concurrents.

Cette technique repose sur la différenciation au niveau du tas des ressources partagées et locales. Les propriétés concernant les ressources partagées sont traitées par l'usage de la *rely-guarantee*. Les propriétés locales sont gérées par l'usage de la logique de séparation, le transfert de ressources étant défini par la définition des interférences.

## 2.3 OUTILS D'ANALYSE DE CODE C

### 2.3.1 Frama-C

FRAMA-C [57] est une plateforme d'analyse de programme écrits en langage C développée au CEA LIST. Elle est conçue de manière modulaire, au sens où elle propose différentes analyses sous la forme de greffons exploitant un noyau qui fournit les fonctionnalités nécessaires pour extraire les informations de base des programmes, en permettant par exemple d'accéder à son arbre de syntaxe abstraite ou aux annotations fournies par l'utilisateur.

Ces fonctionnalités de base reposent sur l'usage de la bibliothèque CIL [71] qui normalise les programmes C (par exemple : transformation de toutes les boucles en `while`, instruction `return` unique pour chaque fonction). FRAMA-C l'étend pour supporter les annotations en ACSL (présenté plus tard dans cette section).

Les analyses fournies peuvent être statiques, dynamiques ou la combinaison des deux. Nous pouvons par exemple citer :

- l'interprétation abstraite (section 2.1.2) avec VALUE [25];

- le calcul de plus faible pré-conditions (section 2.1.4) avec WP;

- la génération automatique de tests (section 2.1.1) avec PATHCRAWLER [96];

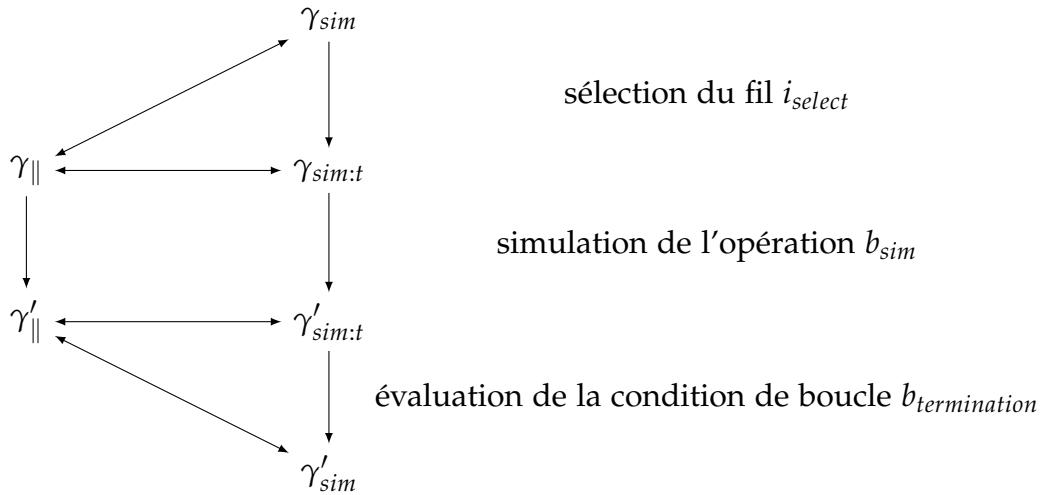

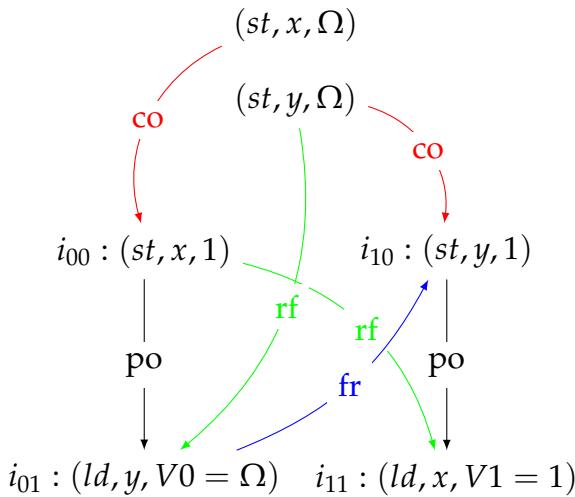

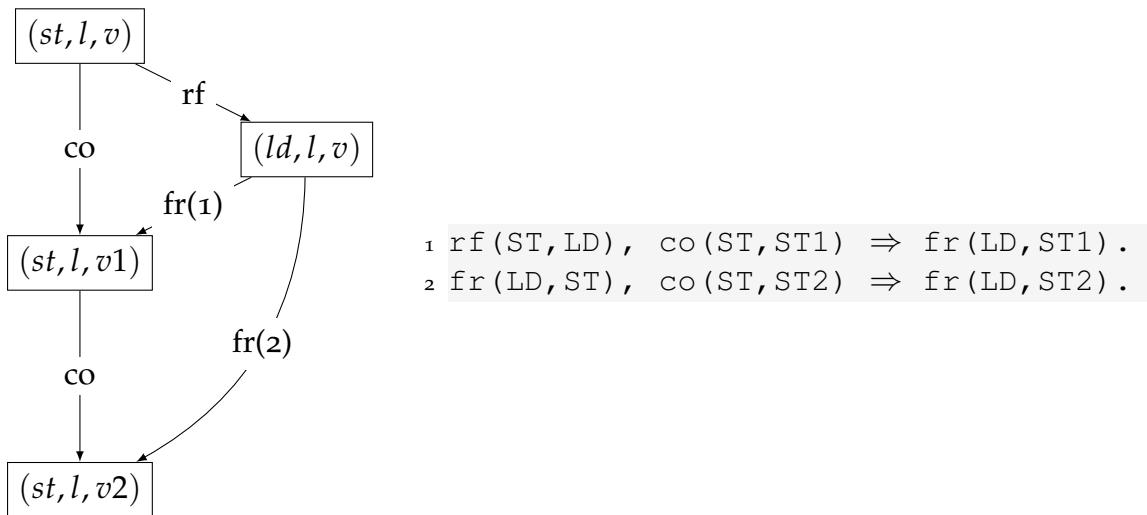

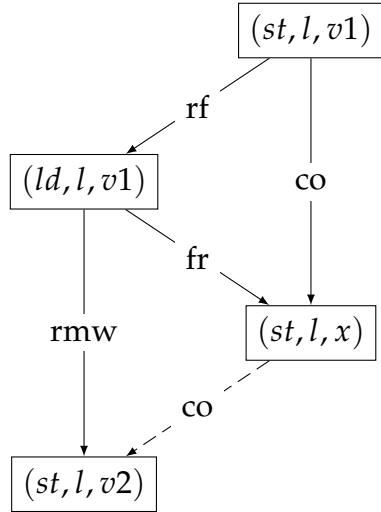

- la combinaison de tests et de preuve avec STADY [78].